| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- freediving

- 프리다이빙입문

- 3급공채

- ai서버

- 트랜지스터

- 반도체 #tsmc #일본반도체정책 #대만일본협력 #기술격차 #문화충돌 #경제안보 #공급망 #국제협력 #산업정책

- 노마드투자자

- 입주전시공

- 독서

- 책

- MOSFET

- 자카리아

- 수학#통계#몬테카를로#montecarlo#확률#과학

- the money book

- 취미

- 사진

- 프리다이버

- 빅테크

- 삼성전자

- 일본#후쿠시마#오염수#방류#방사선#방사능#오염#피폭#발암물질#해산물#논란#뉴스

- w를찾아서

- 파이썬

- 더머니북

- 프리다이빙

- 반도체란

- 직장인

- 반도체기초

- 닉슬립

- brownian

- 반도체

- Today

- Total

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- freediving

- 프리다이빙입문

- 3급공채

- ai서버

- 트랜지스터

- 반도체 #tsmc #일본반도체정책 #대만일본협력 #기술격차 #문화충돌 #경제안보 #공급망 #국제협력 #산업정책

- 노마드투자자

- 입주전시공

- 독서

- 책

- MOSFET

- 자카리아

- 수학#통계#몬테카를로#montecarlo#확률#과학

- the money book

- 취미

- 사진

- 프리다이버

- 빅테크

- 삼성전자

- 일본#후쿠시마#오염수#방류#방사선#방사능#오염#피폭#발암물질#해산물#논란#뉴스

- w를찾아서

- 파이썬

- 더머니북

- 프리다이빙

- 반도체란

- 직장인

- 반도체기초

- 닉슬립

- brownian

- 반도체

- Today

- Total

sean's archive

반도체 기초 - FinFET, GAA, MBCFET, CFET, Forksheet 본문

반도체 기초 - FinFET, GAA, MBCFET, CFET, Forksheet

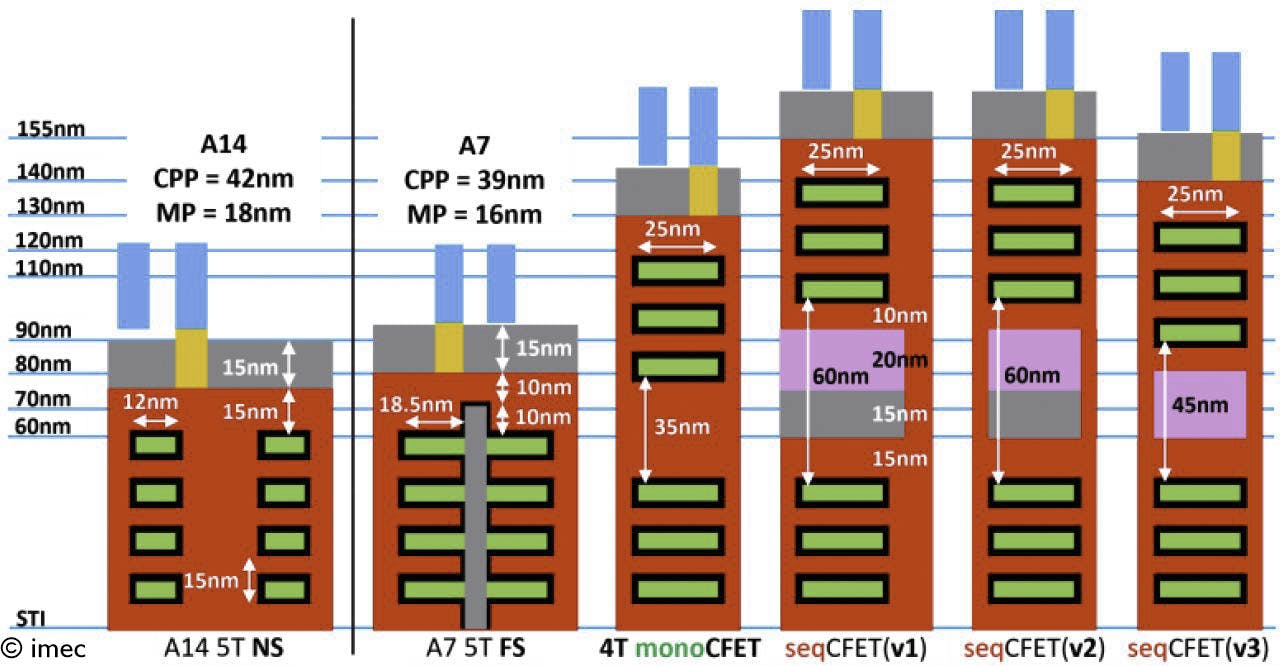

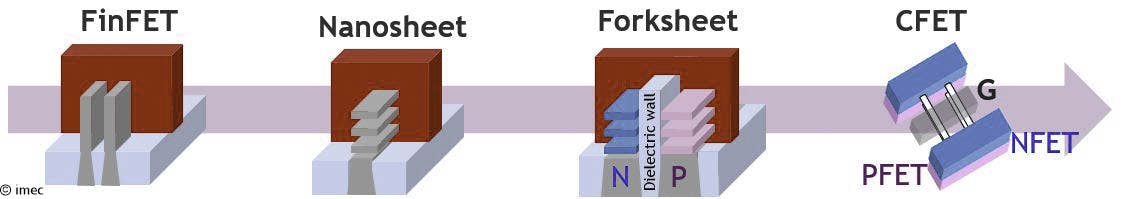

sean in BD 2023. 2. 11. 18:26반도체의 성능, 속도, 양산성을 향상시키기 위해 트랜지스터의 크기를 줄이는 방향으로 연구개발이 이루어져 왔습니다. 하지만 트랜지스터의 크기가 14nm이하로 작아지면서, short channel effect등의 여러 부작용이 나타나게 되었습니다. 채널이 안정적으로 작동할 만큼의 채널 길이가 확보되지 않은 점이 주원인입니다. 이런 문제점을 해결하기 위해서 트랜지스터 구조를 2D가 아닌 3D로 만드는 방향으로 연구가 진행되었습니다.

1. FinFET

트랜지스터의 모양이 물고기의 지느러미인 핀(Fin) 과 닮은 모양이라고 해서, FinFET이라는 이름이 붙었습니다. 소스와 드레인과 기판 부분을 수직방향으로 쭉 늘려놓은 듯한 모습입니다. 2D 트랜지스터에서는 게이트의 한 면이 채널을 형성하지만 FinFET 에서는 세 면에서 동시에 전압을 걸게 됩니다. 그에 따라서 채널 아래쪽으로 흐르던 누설 전류를 개선할 수 있게 되었습니다. 다시 전류의 on/off를 뚜렷하게 구분할 수 있게 된 것입니다. 또한, 누설 전류가 개선됨에 따라 더욱 작은 사이즈의 트랜지스터를 만들 수 있게 되었습니다.

다만 FinFET에서부터는 몇 나노급 이라고 부르는 제품들이 트랜지스터의 사이즈를 의미하는 것은 아니게 되었습니다. 14nm급 2D트랜지스터와, 동급의 FinFET은 제품의 성능과 목적에 따라서 서로 다른 사이즈를 가지고 있을 수 있습니다.

삼성전자의 선단 공정이라 불리는 7nm, 5nm, 4nm 급 제품들이 양산 되고 있는 FinFET 입니다.

2. GAA(Gate All Around), MBCFET

FinFET의 개발 이후 트랜지스터를 더 작고 빠르게 만드는 방향으로 연구가 진행되었습니다. 네 면에서 전압을 걸어서 성능을 더욱 개선한 모양입니다. 게이트(Gate)가 채널을 네 면에서 전부 감싸고 있는 모습(All Around) 이기 때문에 GAA라는 이름이 붙었습니다. FinFET대비 성능이 더욱 개선되었지만 공정 난이도가 급상승하였습니다. 2022년도에 삼성전자에서는 첫 GAA 제품인 3nm급 트랜지스터 양산을 시작하였습니다. 하지만 공정 난이도가 높아 수율은 아직 많이 낮은 것으로 보입니다. TSMC에서는 3nm까지는 FinFET, 2nm급 제품부터 GAA를 적용하겠다고 발표한 상황입니다.

GAA에서도 채널의 모양이 시트(sheet) 같은 모양이고 나노미터(nanometer) 스케일의 크기를 가지고 있는 구조를 나노시트(nanosheet, NS) 라고 합니다. 소스와 드레인의 다리(Bridge) 역할을 하는 채널이 여러 개(Multi) 있으므로 이를 MBC(Multi Bridge Channel) FET 이라고도 합니다.

3. beyond 1nm

여기서부터는 1nm급 이하의 공정 스킴(Scheme)으로, 2027년 이후 (혹은 더 나중에) 양산을 위해 연구가 진행되고 있는 (N+3, N+4, …) 구조들입니다. 반도체 최선단 공정을 연구하는 벨기에 연구소인 IMEC 에서 발표되고 연구중인 구조들 입니다. 삼성전자와 TSMC와 같은 실제 기업에서도 해당 구조에 대한 구체적인 로드맵은 아직 나오지 않은 상황입니다.

3-1. CFET(Complementary FET)

CFET이란 GAA구조의 트랜지스터를 수직으로 쌓아 올려서 만든 구조입니다. 여려 소자를 만들기 위해 NFET과 PFET들이 배치되어 있는데, 이를 빌딩처럼 동일 면적 위에 쌓아 올리게 되면 이론상 두배의 면적 절감 효과를 가져올 수 있습니다. 트랜지스터의 면적을 줄일수록 더 많은 트랜지스터를 같은 면적안에 넣을 수 있고 면적대비 효율이 증가하게 됩니다. 다만 많은 층의 나노시트를 만들면서 생기는 공정 난이도의 증가로 인해 해결해야 할 문제가 너무나 많은 구조 입니다.

3-2. Forksheet

Forksheet는, 나노시트 의 모양이 마치 포크(Fork)처럼 생겼다고 해서 붙은 모양입니다. 긴 나노시트 사이에 절연층을 넣어 반으로 분리시킨 후 한쪽은 NFET, 한쪽은 PFET으로 만든 구조입니다. NFET과 PFET이 거의 붙어있기 때문에 소자의 사이즈를 대폭 줄일 수 있습니다.

4. 개인 생각

AI, 자율주행등 4차 산업혁명의 여러 분야가 비약적으로 발전함에 따라 더 고도화된 반도체 칩의 요구가 늘어나고 있습니다. 현재 3nm급 이하의 제품을 만들 수 있는 회사는 대만의 TSMC와 한국의 삼성전자뿐입니다. 하지만 미국의 Intel 이 2024년에 20A (2nm)급 제품을 만들겠다고 선언해 파운드리 경쟁구도에 긴장감을 더하고 있습니다. 거기에 일본의 주요 대기업 8사가 반도체 산업을 위해 만든 공동 법인인 라피더스(Rapidus) 도 2027년에 2nm급 제품 양산을 선언했습니다.

라피더스는 아직 제품으로 보여준 게 없는데 갑자기 최선단 공정을 양산하겠다고 하니, 성공할 수 있을지 잘 모르겠습니다. 하지만 Intel은 과거 반도체 일인자로서 축적된 경험과 노하우가 있고, Intel 10nm급 제품이 TSMC 7nm급 제품과 비슷하다고 할 정도로 실력도 좋은 편입니다. 무시할 수 없는 막강한 경쟁자가 나타났으니, 한국에 사는 저로서는, 반도체 주도권을 미국에 뺏기지 않을까 걱정되면서도 반도체 엔지니어의 몸값이 오르지 않을까 하는 걱정반 기대반인 심정을 가지고 있습니다.

P.S. 솔직히 개인적으로 한국에서 일하는 반도체, 디스플레이, 배터리 연구개발을 하고 있는 엔지니어들은.. 이직 대안이 없다는 이유로 인해 하는 일의 중요성에 비해 제 몸값을 받지 못하고 있다고 생각합니다.

'반도체 엔지니어 (Semiconductor)' 카테고리의 다른 글

| SRAM 의 구성 및 동작원리 (2) | 2023.08.27 |

|---|---|

| 반도체 기초 - CMOS, Inverter, Ring oscillator (2) | 2023.02.17 |

| 반도체 기초 - 트랜지스터, MOSFET (0) | 2023.02.08 |

| 반도체 기초 - 진성반도체, P형, N형, PN접합 (0) | 2023.02.01 |

| 반도체 기초 - 반도체란 무엇인가 (0) | 2023.01.23 |